第1章 计算机系统概述

分类发展

SISD(单指令流单数据流系统)

SIMD(单指令多数据流)

MISD(多指令单数据流)

MIMD(多指令多数据流)

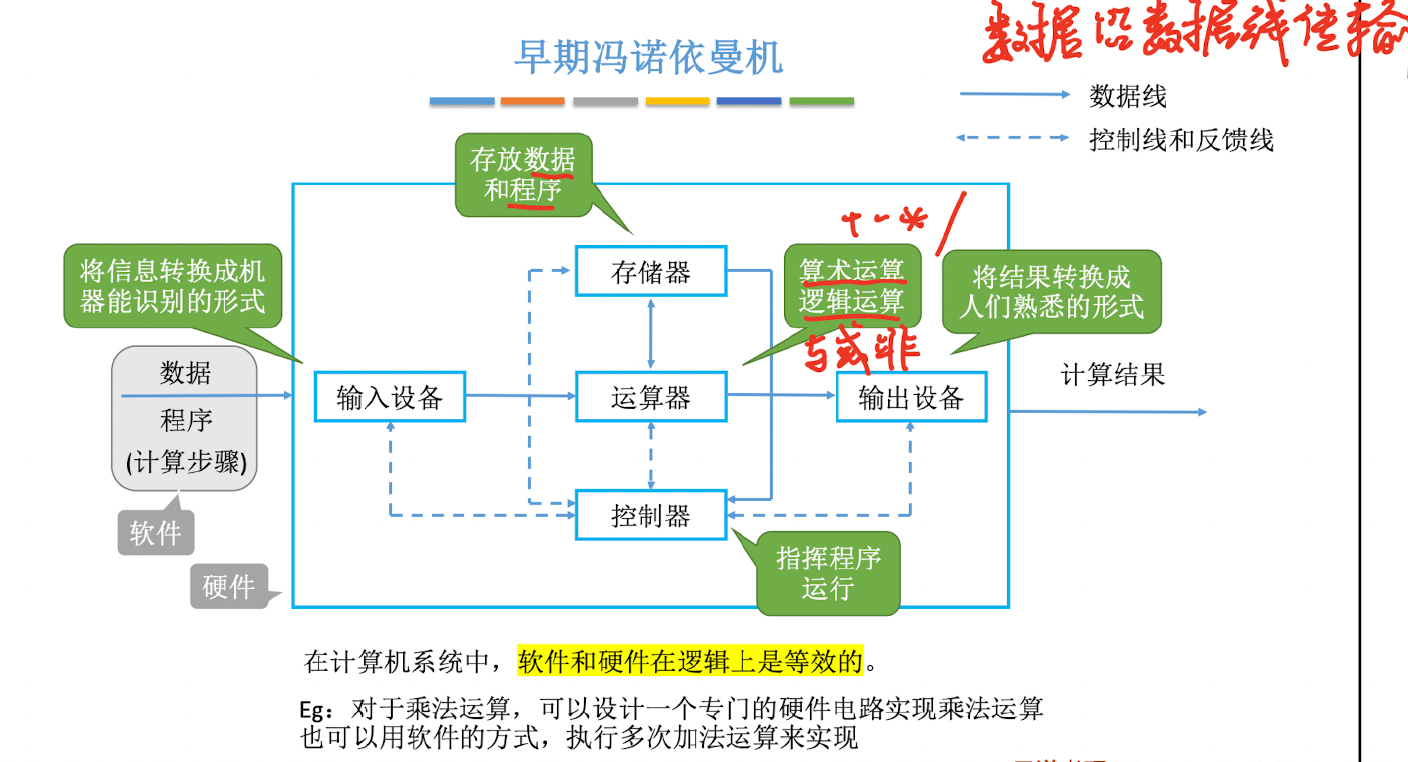

计算机由硬件和软件组成

冯诺伊曼计算机:以运算器为核心、存储器、控制器、输入设备、输出设备

现代计算机:以存储器为核心,CPU=运算器+控制器

计算机功能部件

存储器

- 主存储器(CPU直接访问,通常为内存)

存储字长,一个存储单元可以存储一串二进制代码,这串代码成为存储字,位数称为存储字长。

地址寄存器(MAR):在CPU中,位数等于PC

数据存储器(MDR):在CPU中,位数等于存储字长

- 外存

运算器

- ALU(算术逻辑单元)

- 通用寄存器

- ACC(累加寄存器)

- MQ(乘商寄存器)

- X(操作数寄存器)

- IX(变址寄存器)寻址

- BR(基址寄存器)寻址

- PSW(程序状态寄存器)

控制器

- PC(程序计数器)

- IR(指令寄存器)

- CU(控制单元)

计算机软件分类

系统软件、应用软件

**三个级别的语言:**机器语言、汇编语言、高级语言

**翻译程序:**编译程序(高级 to 汇编 or 机器)、汇编程序(汇编 to 机器)、解释程序(翻成机器,翻译一条、执行一条)

计算机工作过程

程序和数据装入主存

把原程序转换成可执行文件

- 预编译(cpp,.i)

- 编译(ccl,.s)

- 汇编(as,.o)

- 链接(ld)

性能指标

容量

- 机器字长

- 存储字长和指令字长

- 主存容量

1 | 存储单元个数 * 存储字长 |

MAR反应存储单元个数、MDR反应每个存储单元大小

*数据通路带宽(数据字长)**:数据总线一次所能进行传送信息的位数

速度

吞吐量、响应时间、时钟周期、主频(CPU时钟频率)、CPI、CPU执行时间、IPS、MELOPS、GFLOPS、TFLOPS,看书吧

$$

平均CPU=\frac{主频}{IPS}

$$

$$

CPU时钟频率(主频)=\frac{1}{CPU时钟周期}(Hz)

$$

计算之前一定要确保单位换算一致

第2章 数据的表示和运算

真他妈傻逼,啥破专业考他妈单位换算

机器数的定点表示

- 定点小数:表示范围 $-(1-2^n-n)$~$1-2^{-n}$,第一位是符号位,纯小数

定点数表示

原码

反码

对于正数,反码与原码的表示相同,对于负数,原码符号位不变,数值部分按位取反

补码

对于正数,补码与原码的表示相同,对于负数,原码符号位不变,数值部分按位取反,末尾+1(取反加一),补码0表示唯一

移码

在补码的基础上将符号位取反,移码只能用于表示整数

第3章 存储系统

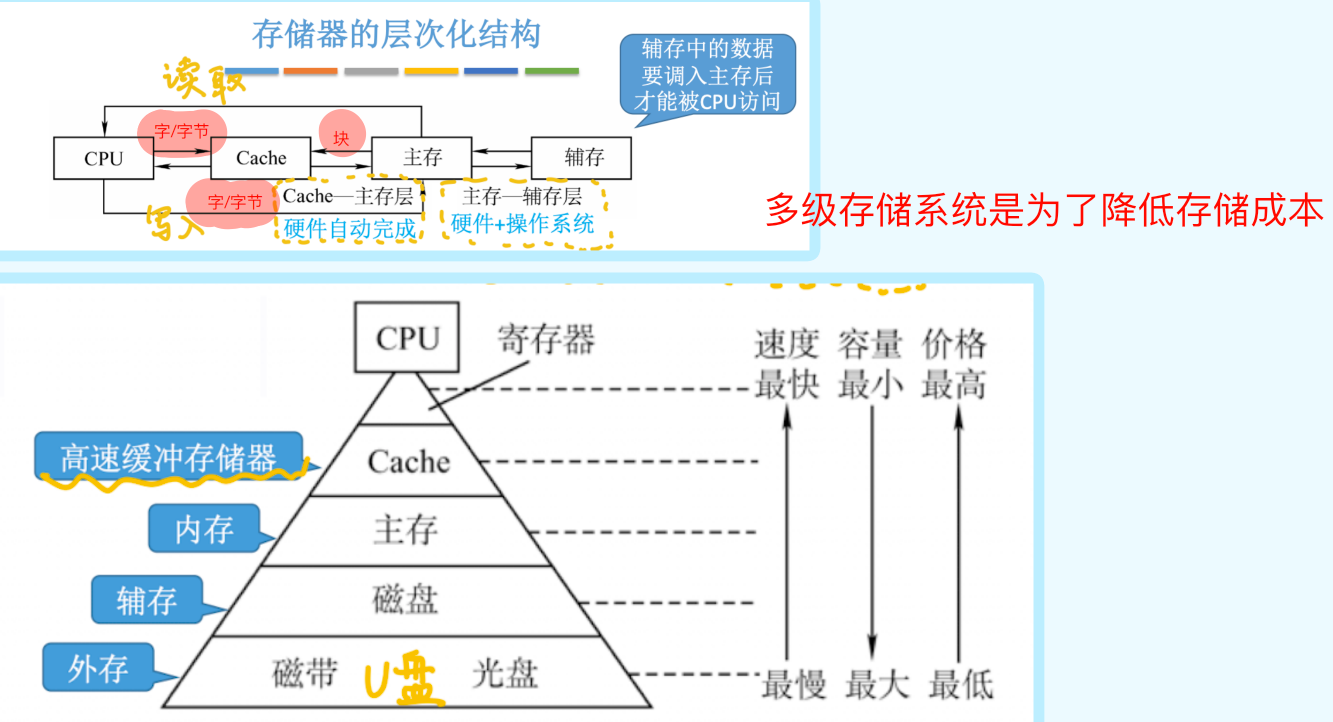

层次化结构

主存-辅存:硬件+操作系统实现,实现虚拟存储系统,解决了高速主存容量不够的问题

Cache-主存:硬件实现,解决了主存与CPU速度不匹配的问题

存储器的分类

按在计算机中的作用(层次)分类

- 高速缓存Cache

- 主存(内存)

- 辅存(外存)

按存取方式分类

- 随机存取存储器(RAM)

- SRAM(静态RAM)

- DRAM(动态RAM)

- 按照地址访问存储单元,任何一个存储单元的内容可以随机存取,存取时间与单元的物理位置无关

- 顺序存取存储器(SAM)

- 存储容量大,存取速度慢

- e.g:磁带存储器

- 直接存取存储器(DAM)

- 特点:存取方式兼有随机访问和顺序存储的特点,首先直接选取所需信息所在区域,然后按照顺序方式来进行存取

- e.g:磁盘存储器

- 按内容访问存储器CAM/相联存储器AM

- e.g:快表就是由CAM实现的

按信息的可保存性分类

-

- 后存储信息是否消失

- 易失性存储器RAM:主存、Cache

- 非易失性存储器ROM:磁表面存储器和光存储器

- 信息读出后是否被破坏

- 破坏性读出:如DRAM芯片,读出数据后要进行重写

- 非破坏性读出:如SRAM芯片、磁盘、光盘

信息可更改性

- 读写存储器(Read/WriteMemory):即可读、可写

- 只读存储器(Read OnlyMemory,ROM):只能读

性能指标

- 存储容量:存储字数x字长(如1Mx8位)

- 单位成本:每位价格=总成本/总容量

- 存储速度

- 数据传输率=数据的宽度/存储周期

- 存储周期(读写周期/访问周期)=存取时间+恢复时间

- 存取时间:从启动一次存储器操作到完成该操作的时间

- 存储周期:它是指存储器进行一次完整的读写操作所需的全部时间,即连续两次独立地访问存储器操作(读或写操作)时间所需的最小时间间隔

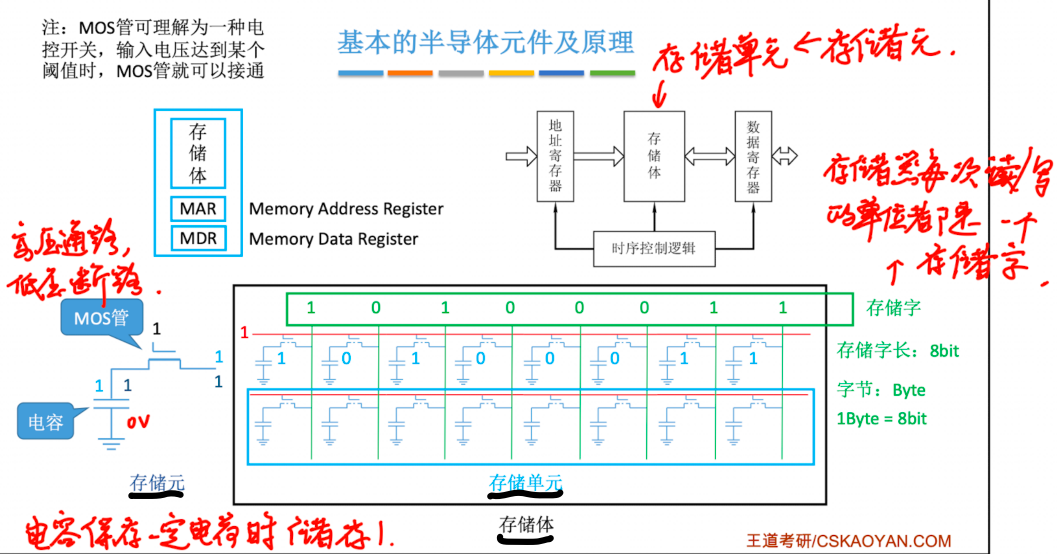

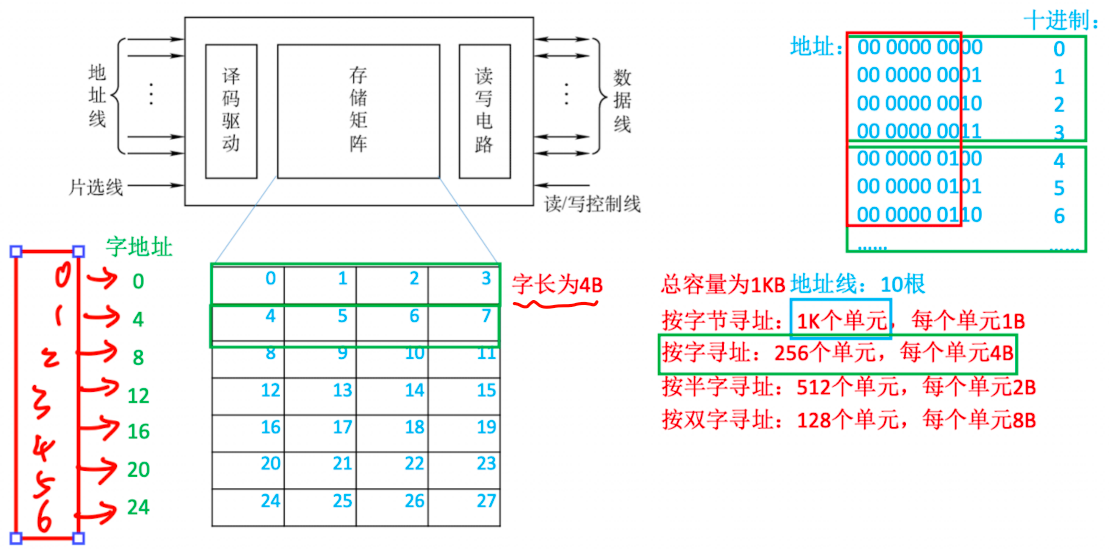

主存器的基本组成

基本元件

- 存储元

- MOS管:作为通电“开关”

- 电容:存储电荷(即存储二进制0/1)

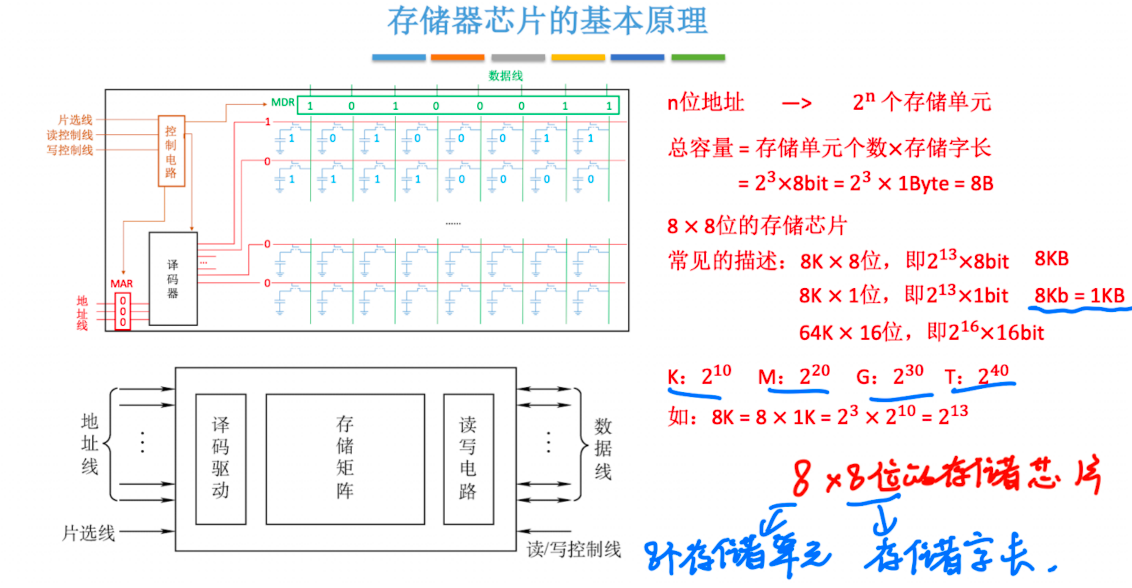

存储芯片的结构

译码驱动电路:译码器将地址信号转换为字选通线的高低电平

存储矩阵(存储体):有多个存储单元构成,每个存储单元又由多个存储元构成

读写电路:每次读/写一个存储字(存储器读写的单位是存储字),存储字:一个存储单元所存储的二进制数据宽度

地址线:数据线、片选线、读写控制线

寻址

现代计算机中通常按照字节来编址

寻址:按字节寻址、按字寻址、按半字寻址、按双字寻址

半导体随机存储器SRAM和DRAM

半导体存储芯片基本结构

片选线 CS/CE(低电平有效)、读写控制线 WE(低电平写,高电平读)

SRAM的芯片结构

- 存储体

- 地址译码器(地址译码方式)

- 一维译码:线选法或单译码法

- 二维译码:重合法或双译码法

- 驱动器

- I/O控制电路

- 片选控制信号

- 读写控制信号

DRAM和SRAM比较

分别是动态RAM和静态RAM

SRAM采用六管静态MOS管存储元件

DRAM采用单管动态MOS管存储元件

| 类型特点 | SRAM(静态(RAM) | DRAM(动态RAM) |

|---|---|---|

| 存储信息 | 触发器(双稳态) | 电容(栅极) |

| 破坏性读出 | 非破坏性读出 | 破坏性读出 |

| 读写后需要重写 | 不需要 | 需要 |

| 运行速度 | 快 | 慢 |

| 集成度 | 低 | 高 |

| 发热量 | 大 | 小 |

| 存储成本 | 高 | 低 |

| 易失/非易失性存储器 | 易失 | 易失 |

| 需要刷新 | 不需要更新 | 需要更新 |

| 送行列地址 | 同时送 | 分两次送 |

| 常用于 | Cache | 主存 |

DRAM工作原理

半导体随机存储器ROM

第4章 指令系统

机器指令是计算机运行的最小功能单位

指令集:一台计算机所有指令的集合构成该指令的指令系统

指令的基本格式

| OP | 寻址特征 | 形式地址A |

|---|

OP+A(操作码字段+地址码字段)

零地址指令:OP,不需要操作数的指令,零地址的运算类指令

一地址指令:OP+A,

- 只有目的操作数的单操作指令

- 只需要单操作数,如加1、减1、取反、求补

- 指令含义:OP(A1)->A1

- 隐含目的地址的双操作指令

- 需要两个操作数,但其中一个操作数隐含在某个寄存器

- 指令含义:(ACC)OP(A1)->ACC

二地址指令:OP+A1(源操作数)+A2(目的操作数),结果默认存回A1

- 常用于需要两个操作数的算术运算、逻辑运算相关指令

- 指令含义:(A1)OP(A2)->A1

- 完成一条指令需要访存4次,取指->读A1->读A2->写A1

三地址指令:OP+A1+A2+A3(结果),结果存入A3中

- 指令含义:(A1)OP(A2)->A3

四地址指令:OP+A1+A2+A3(结果)+A4(下址)

- 指令含义:(A1)OP(A2)->A3

指令按长度分类

指令字长:一条指令的总长度

机器字长:CPU进行一次整数运算所能处理的二进制数据的位数

存储字长:一个存储单元中的二进制代码位数

半字长指令、单字长指令、双字长指令

定长指令结构:指令系统中所有指令的长度都相等(RISC)

变长指令结构:指令系统中各种指令的长度不等(CISC)

操作码

- 可变长操作码

- 定长操作码

指令-按操作类型分类

数据传送类

数据传输:进行主存与CPU之间的数据传送

LOAD:把存储器中的数据放到寄存器中

STORE:把寄存器中的数据放到存储器中

MOVE:存储器之间的传送

运算类

算术运算:加、减、乘、除、增1、减1、求补、浮点运算、十进制运算

- 加(ADD)、减(SUB)、比较(CMP)、乘(MUL)、除(DIV)、加1(INC)、减1(DEC)

逻辑运算:与、或、非、异或、位操作、位测试、位清楚、位求反

- 与(AND)、或(OR)、取反(NOT)、异或(XOR)

移位操作

算数移位、逻辑移位、循环移位

转移操作

程序控制类:改变程序执行的顺序

无条件转移(JMP):在任何鲁棒下都会执行转移操作

条件转移:

- 指令:转移条件

- JZ:结果为0

- J0:结果溢出

- JC:结果有进位

- BRANCH

调用和返回:CALL、RETURN(RET)

陷阱(Trap)与陷阱指令

输入输出操作

输入输出类(I/O),进行CPU和I/O设备之间的数据传送

寻址方式

指令寻址:寻找下一条执行的指令地址称为指令寻址

数据寻址:确定本条指令的地址码指明的真实地址,寻找操作数的地址

指令寻址:下一条预执行指令的地址(PC给出)

- 顺序寻址:程序计数器PC+1,自动生成下一条

- 跳跃寻址:执行转移类指令导致PC值发生改变

- 转移类指令有:JMP、CALL、RET、JL、JE、JLE

数据寻址:

- 指令格式:

- 一地址指令:操作数+寻址特征+形式地址A

- 二地址指令:操作码+寻址特征+形式地址A1+寻址特征+形式地址A2

- 寻址特征:确定使用哪种方法寻址

数据寻址方式

直接寻址

间接寻址

寄存器寻址

寄存器间接寻址

隐含寻址

立即数寻址

偏移寻址

堆栈寻址

汇编语言

这个很熟了,简单复盘下指令吧

CISC和RISC

第5章 中央处理器

CPU由=运算器+控制器+寄存器组成,分为指令控制(PC、IR)、操作控制(CU)、时间控制(时序电路)、数据加工(ALU、寄存器)、中断处理(中断系统)

运算器:对数据进行处理

控制器:取指令、分析指令、执行操作、中断处理

按功能分::运算器和控制器(合并为中央处理器CPU)

从逻辑上分:控制单元、运算单元、存储单元

CPU的基本结构

运算器的基本结构

- 算术逻辑单元

- 通用寄存器组

- 暂存寄存器

- 累加寄存器ACC

- 程序状态字寄存器PSW

- 移位器

- 计数器

控制器的基本结构

- 程序计数器PC

- 指令寄存器IR

- 指令译码器IE

- 微操作信号发生器

- 时序系统

- 存储器地址寄存器MAR

- 存储器数据寄存器MDR

指令执行过程

指令周期:一个完整的指令周期包括取址、间址、执行和中断

机器周期=CPU周期:也就是完成指令中某一步操作所需要的时间,其中也包括若干个时钟周期

时钟周期=节拍=T周期=CPU时钟周期,是CPU操作的最基本单位

机器周期分为鼎定长机器周期和不定场的机器周期

取址周期

根据PC中的地址从主存中取出指令放入IR中,并且PC+1

- (PC)->MAR

- 将MAR通过地址总线->内存

- 1->R,CU发出读信号,通过控制总线->内存

- M(MAR)->MDR,将要执行指令从存储器读到数据寄存器

- (MDR)->IR,要执行的指令打入指令寄存器

- OP(IR)->CU

- (PC)+1->PC

间指周期

去除操作数的有效地址,将指令地址码送到MAR并送到地址总线,CU向存储器发读命令,将有效地址放到MDR中

- AD(IR)->MAR

- 将MAR内容通过地址总线->内存

- 1->R

- M(MAR)->MDR

执行周期

取出操作数并执行指令,无统一数据流向,不同指令的执行周期操作不同。

中断周期

指令执行方案

单指令周期:方便设计电路,所有指令都在固定的时钟周期内完成,指令之间串行执行

多指令周期:需要更复杂的硬件设计,可选用不同个数的时钟周期来完成不同指令的执行,执行之间串行执行

流水线方案:指令之间并行执行

数据通路的功能和基本结构

数据通路的功能:

- 数据通路:数据在功能部件之间的传送路径成为数据通路

- 路径上的部件称为数据通路部件

基本结构

CPU内部单总线方式

将所有寄存器的输入端和输出端都连接到一条公共通路上,结构简单,但容易发生冲突

CPU内部多总线方式

将所有寄存器的输入端和输出端都连接到多个公共线路上,数据的传递可以同时进行

专用数据通路方式

通过根据指令执行过程中数据和地址流动的方向来布置连接线路,避免采用共享的总线。

CPU数据的传送

寄存器之间的数据传送

主存与CPU之间的数据传送

执行算术或逻辑运算